O-RAN Distributed Unit Low Layers (ODULOW) | |

|---|---|

PTL | |

Summary | Focus on L1 functional blocks development according to WGs specification. |

Project | |

Weekly Meetings | TBD, anyone is interested in O-DU Low project, would like to get more information, would like to know how to participant, please no hesitate to contact zhimin.yuan@intel or raise any questions through this wiki page. |

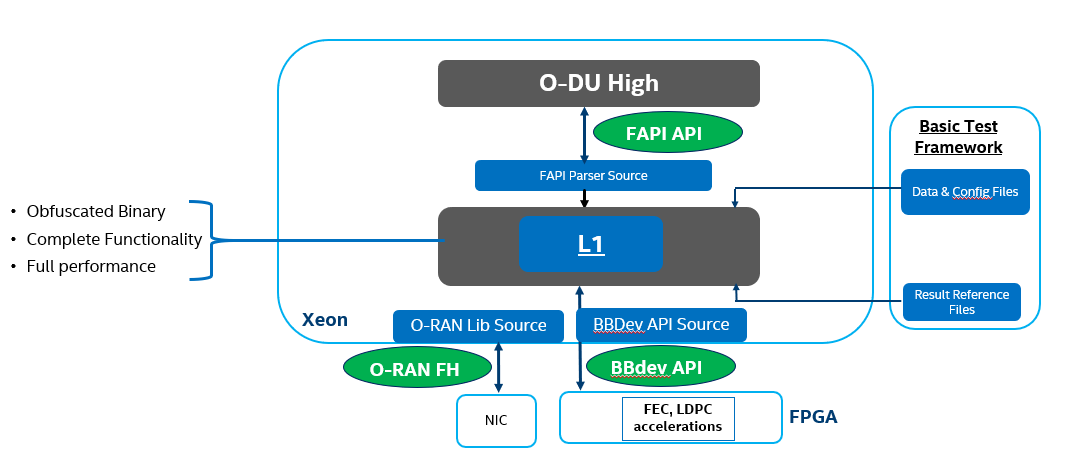

Current L1 functional development mainly focus on the open interface development, three interfaces will be involved to interact with L1 as below:

- Interface between L1 and Front haul, it will adopt the WG4 specification for the CUS plane communication.

- Interface between O-DU Low and O-DU High, FAPI interface will be adopt according to WG8 AAL specification.

- Interface between O-DU Low and accelerator, it's the hot topic in WG6 now, DPDK BBDev was adopted as previous design, it will follow the WG6 definition after WG6 specification is finalized.

For amber release, O-RAN FH library was contributed by Intel as seed code, BBDev API was already open source in DPDK community, please find detail API information in http://doc.dpdk.org/api/rte__bbdev_8h.html, FAPI API is under development.

O-RAN FH Lib is developed according to the O-RAN WG4 specification. It performs communication between the lower-layer split Central Unit (lls-CU) and RU and consists of multiple HW and SW components. Logical representation of HW and SW components is shown as below diagram:

From the hardware perspective, two networking ports are used to communicate to the Front Haul and Back (Mid) Haul network as well as to receive PTP synchronization. The system timer is used to provide “sense” of time to the gNB application.

From Software perspective the following components are used:

- Linux PTP provides synchronization of system timer to GPS time.

- Ptp4l is used to synchronize oscillator on Network Interface Controller (NIC) to PTP GM.

- Phc2sys is used to synchronize system timer to oscillator on NIC.

- DPDK to provide interface to Ethernet port.

- O-RAN FH library is built on top of DPDK to perform U-plane and C-plane functionality according to the O-RAN WG4 specification.

- 5G NR PHY(L1) uses the O-RAN FH library to access interface to RU. The interface between O-RAN FH library and 5G NR PHY is defined to communicate TTI event, symbol time, C-plane information as well as IQ sample data.

- 5G NR PHY communicates with L2+ application using the set of MAC/PHY APIs and the shared memory interface defined as WLS.

- L2+ in turn can use Back (Mid) Haul networking port to connect to CU unit in context of 3GPP specification.